# **RBSP EFW**

### Data Controller Board (DCB) FPGA Specification & Functional Description

### RBSP\_EFW\_DCB\_0010

Dorothy Gordon, U.C Berkeley RBSP EFW DCB FPGA Engineer

Peter Harvey, U.C Berkeley RBSP EFW FSW

Michael Ludlam, U.C. Berkeley RBSP EFW Systems Engineer

## **RBSP EFW**

# Data Controller Board (DCB) FPGA Specification & Functional Description RBSP\_EFW\_DCB\_0010

23 November 2009

#### **References.**

- 1. Interface Control Document (ICD) for the EFW Investigation, Applied Physics Laboratory (Dwg No. 7417-9083)

- 2. THEMIS Data Controller Board Specification and Functional Description (thm-dcb-001, Rev. A.06, 11 October 2004)

- 3. Zilog Z8400/Z84C00 NMOS/CMOS Z80 Specification

- 4. CZ80CPU Synthesizable HDL Core Specification (CZ80CPU-DES-1H18N00S00-200), Evatronix SA, April 26, 2007

- 5. RBSP\_EFW\_DCB\_003E\_Specification: Digital Control Board (DCB) Specification

- 6. RBSP\_EFW\_BPL\_001M\_Specification: IDPU Backplane Specification

- 7. RBSP EFW PCB Logic, Rev. B, June 23, 2008

- 8. RBSP\_EFW\_BEB\_SCH\_002A, Rev. A

- 9. Boom Electronics Board (BEB) Specification, RBSP\_EFW\_BEB\_001F

- 10. AD5544/AD5554 DAC Specification, Analog Devices, 2004, Rev. A

- 11. NAND FLASH Memory MT29F16G08--- Specification, Rev. B, 2/07

# Table of Contents

| 1.0 | Introd | luction                                                                               | 5  |

|-----|--------|---------------------------------------------------------------------------------------|----|

| 2.0 | Subsy  | stem Descriptions                                                                     | 7  |

|     | 2.1    | Clocks                                                                                |    |

|     | 2.2    | Reset                                                                                 |    |

|     | 2.3    | CPU                                                                                   |    |

|     | 2.0    | 2.3.1 Debug Interface                                                                 |    |

|     |        | 2.3.2 Interrupts                                                                      |    |

|     | 2.4    | CPU Memory                                                                            |    |

|     |        | 2.4.1 CPU Memory Map                                                                  |    |

|     |        | 2.4.2 CPU I/O Space                                                                   |    |

|     | 2.5    | Memory Bus Control/Arbitration                                                        | 23 |

|     | 2.6    | Bulk Memory - SDRAM                                                                   | 24 |

|     |        | 2.6.1 SDRAM Error Correction Circuitry (ECC)                                          | 24 |

|     | 2.7    | FLASH Memory                                                                          | 26 |

|     |        | 2.7.1 FLASH Addressing                                                                | 27 |

|     |        | 2.7.2 FLASH Control                                                                   |    |

|     |        | 2.7.3 FLASH ECC                                                                       |    |

|     |        | 2.7.4 FLASH Interrupt                                                                 |    |

|     | •      | 2.7.5 FLASH Diagnostic Mode                                                           |    |

|     | 2.8    | Timekeeping                                                                           |    |

|     |        | 2.8.1 Timebase Counter                                                                |    |

|     | •      | 2.8.2 S/C Timing Signals (1PPS and Spin Pulse)                                        |    |

|     | 2.9    | Housekeeping Subsystem                                                                |    |

|     | 2.10   | PCB Interface                                                                         |    |

|     | 2.11   | BEB Interface                                                                         |    |

|     |        | 2.11.1 BEB Analog Mux Controls                                                        |    |

|     |        | 2.11.2 BEB AC Test Stimulus                                                           |    |

|     | 2.12   | 2.11.3 BEB DAC Controls<br>DFB Interface                                              |    |

|     | 2.12   |                                                                                       |    |

|     |        | <ul><li>2.12.1 DFB Command Interface</li><li>2.12.2 DFB Telemetry Interface</li></ul> |    |

|     |        | 2.12.2 DFD Telementy Internace                                                        |    |

|     | 2.13   | Spacecraft Interface                                                                  |    |

|     | 0      | 2.13.1 UARTs (CMD and TLM)                                                            |    |

|     |        | 2.13.2 S/C Command DMA Interface                                                      |    |

|     |        | 2.13.3 S/C Telemetry DMA Interface                                                    |    |

|     |        | -                                                                                     |    |

### **Document Revision History**

| <b>Revision Number</b> | Date              | Change Summary                                                                                                                                                                                                                                                                                                                                                |

|------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А                      | 11 February 2008  | Initial Draft                                                                                                                                                                                                                                                                                                                                                 |

| В                      | 04 March 2008     | Incremental changes                                                                                                                                                                                                                                                                                                                                           |

| С                      | 24 March 2008     | Additional design details                                                                                                                                                                                                                                                                                                                                     |

| D                      | 18 April 2008     | References to data repository removed (changed to FLASH); references<br>to SSR removed (changed to SDRAM); addition of Baud Rate Selection<br>for telemetry, protoboard debug hooks (Diagnostic Switch and LEDs);<br>reduction of telemetry buffer page size to 4Kbytes, reorganization of the<br>DFB DMA channel; additional design details and corrections. |

| E                      | 10 June 2008      | Added debug UART details, minor corrections                                                                                                                                                                                                                                                                                                                   |

|                        |                   | Changed document name (added FPGA to title)                                                                                                                                                                                                                                                                                                                   |

|                        |                   | Added Latchup Protection Description                                                                                                                                                                                                                                                                                                                          |

|                        |                   | Modified FLASH Power-Switching                                                                                                                                                                                                                                                                                                                                |

|                        |                   | Removed Housekeeping Mux Channel Assignment Table (now included in Reference 5).                                                                                                                                                                                                                                                                              |

| F                      | 06 August 2008    | Added debug UART facility for S/C Interface (temporary for initial test)                                                                                                                                                                                                                                                                                      |

|                        |                   | Added memory mapped I/F for FLASH and FLASH I/O based controls                                                                                                                                                                                                                                                                                                |

|                        |                   | Modified DFB-DMA: as of this revision all channels can be directed to either SDRAM or SRAM.                                                                                                                                                                                                                                                                   |

| G                      | 09 September 2008 | Removed Latchup Protection                                                                                                                                                                                                                                                                                                                                    |

|                        |                   | Slight modification to DFB CDI Status added error detect                                                                                                                                                                                                                                                                                                      |

|                        |                   | Reduced # of DFB DMA channels to 16 (APIDs 0x40 - 0x4F)                                                                                                                                                                                                                                                                                                       |

|                        |                   | Changed DFB DMA High Rate DMA Swap Option to 128Hz                                                                                                                                                                                                                                                                                                            |

|                        |                   | Added DFB DMA buffer overflow error detection                                                                                                                                                                                                                                                                                                                 |

|                        |                   | S/C Telemetry I/F simplification (removed double-buffering)                                                                                                                                                                                                                                                                                                   |

| Н                      | 21 October 2008   | UART-DMA page size reduced to 1Kbyte                                                                                                                                                                                                                                                                                                                          |

|                        |                   | Added details relating to DFB DMA and S/C DMA Subsystems                                                                                                                                                                                                                                                                                                      |

| Ι                      | 18 November 2008  | Added details relating to the BEB and PCB Interfaces                                                                                                                                                                                                                                                                                                          |

|                        |                   | Added Board-ID and a few minor comments and modifications                                                                                                                                                                                                                                                                                                     |

| J                      | 10 December 2008  | Modified BEB DAC Interface                                                                                                                                                                                                                                                                                                                                    |

|                        |                   | Defined ETU/FLIGHT Debug Interface                                                                                                                                                                                                                                                                                                                            |

|                        |                   | Added FLASH subsystem details                                                                                                                                                                                                                                                                                                                                 |

| K                      | 27 January 2009   | FLASH Subsystem description updated                                                                                                                                                                                                                                                                                                                           |

| L                      | 27 February 2009  | FLASH Subsystem Error Detection and Diagnostic Logic detailed                                                                                                                                                                                                                                                                                                 |

|                        |                   | SDRAM PowerOn Cntl restored to the DCBCtl Reg Description                                                                                                                                                                                                                                                                                                     |

| М                      | 18 May 2009       | DIAG LEDs increased to 8-bit wide, DIAG SWITCH eliminated                                                                                                                                                                                                                                                                                                     |

|                        |                   | SDRAM ECC Multibit and Single Bit error counters cleared at the beginning of each scrub cycle                                                                                                                                                                                                                                                                 |

|                        |                   | Corresponds to Rev. C3                                                                                                                                                                                                                                                                                                                                        |

| N                      | 31 Aug 2009       | Changed LVPS- SYNCH-CLOCK from 839KHz to 799KHz                                                                                                                                                                                                                                                                                                               |

|                        |                   | Corresponds to Rev. C4                                                                                                                                                                                                                                                                                                                                        |

| 0                      | 23 Nov 2009       | Eliminated S/C Telemetry High-speed Mode & Minor Corrections to document                                                                                                                                                                                                                                                                                      |

|                        |                   | Corresponds to Rev. C5                                                                                                                                                                                                                                                                                                                                        |

### **1.0 Introduction**

I

The Data Controller Board (DCB) is a component of the RBSP-EFW IDPU. It receives commands from the Spacecraft Processor and manages the Electric Field Instrument (EFI). The DCB communicates with the BEB, DFB and PCB subsystems via custom interfaces, receiving/ storing data and forwarding instrument commands and register loads.

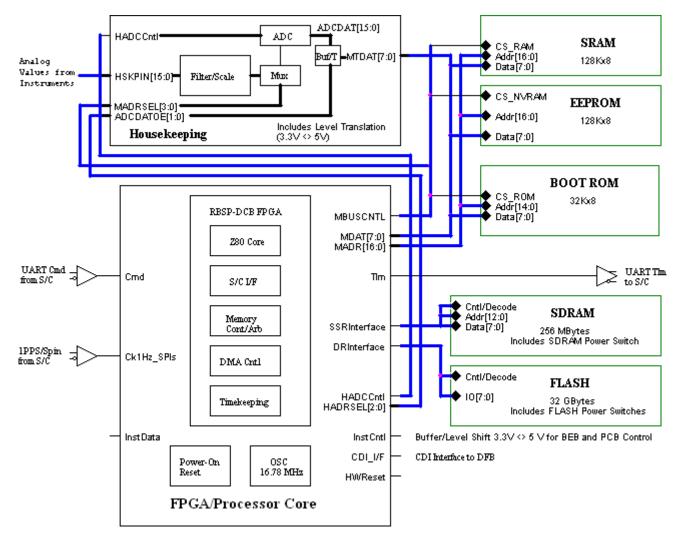

FIGURE 1. DCB: Overall Block Diagram

Figure 1 shows an overview of the main subsystems comprising the DCB. The microprocessor is a Z80 8-bit microcontroller (implemented in the FPGA via an IP Core). The flight FPGA is the Actel RTAX2000S, with the CAST Inc IP core instantiated as the CPU.

The CPU and logic subsystems are supported by an 32Kx8 Boot Rom, SEU-Immune Static RAM and EEPROM. (NOTE: the 128Kx8 SRAM shown is segmented and shared by the FPGA subsystems.) The FPGA handles the processor bus control and provides registers for accessing the various sections of memory. Also included in the FPGA are the Instrument I/Fs, the SDRAM controller, the FLASH Memory Controller, Error Detection/ Correction for SDRAM and FLASH, the S/C Interface Logic, DMA and data management control, analog housekeeping control, and timing/time-tagging support.

The DCB resides on a 6U VME board, connecting to the backplane via the standard VME 96 pin connector. Power is received through the backplane connection, which is also used to communicate with the following IDPU based instrument interfaces and subsystems:

<u>The Digital Fields Board</u> (DFB) - IDPU resident interface board which talks to the EFI, SCM and MAG FGM. The Interface Board also performs processing and programmable filtering.

<u>The Boom Electronics Board</u> (BEB) - IDPU resident interface board, controls sensor biasing and modes. The BEB receives low level digital control signals and outputs analog telemetry.

<u>The Power Supply and Control Board</u> (LVPS/PCB) - IDPU resident subsystem includes the Boom Deployment Power Switching. The PCB receives low level digital control signals and outputs analog telemetry.

A harness is used to connect the DCB to the C&DH Board (S/C Processor). This C&DH Interface contains a UART based Telemetry Interface (115.2KBaud), a timing signal (1Hz Clock and "Spin Pulse"), and a UART (115.2Kbaud) based Command Interface.

#### 2.0 Subsystem Descriptions

### 2.1 Clocks

The DCB receives one clock from the spacecraft, a 1 Hz tick (1PPS), correlated to the S/C time broadcast. (The 1PPS line is also used to transmit the SpinPulse. The differentiation is accomplished via pulse-width coding.)

The DCB internal timebase is set by a local oscillator (SCLK = 16.78MHz) which is used by the FPGA as the overall system clock. SCLK is further divided to generate the timebase clock used by the DFB(8.39 MHz), a 256HZ CPU Interrupt, and a 1Hz Synch (CLK1HZ) used by the DFB and DCB. A derivative of SCLK, 799KHz, 52.4%(HI)/47.6%(LO) duty cycle, provides a power converter synch clock.

#### 2.2 Reset

The overall DCB reset, generated by the FPGA, is an OR of two sources: a power-on hardware reset (generated by an RC delay network and AC14 gate) and a watchdog reset.

A watchdog reset pulse (duration =  $3 \mu s$ ) is generated if the CPU does not write to the Watchdog Reset Clear register for a period of 3 seconds (3 ticks of the internally generated 1 Hz clock). An external jumper is provided, allowing for disabling the watchdog during debug. If the jumper is installed, the watchdog reset is disabled; otherwise the watchdog reset is always enabled. Watchdog Reset detect is available as status.

### 2.3 CPU

The CPU is an FPGA based Z80 microcontroller, running at 16.78MHz. Support circuitry in the FPGA includes bus timing and memory/arbitration/decode logic.

### 2.3.1 Debug Interface

The DCB debug connections allow for external diagnostic peripherals and monitoring of the CPU Bus.

The debug subsystem includes a RS232 compatible UART, mapped into Z80 I/O space and decoupled via 128 byte FIFOs in both directions. The Debug UARTs are detailed in their Register descriptions, starting on page 20.

The DCB prototype has been constructed using a reprogrammable Actel FPGA (the A3P1000, a ProASIC3 FLASH based device). The prototype board (different FPGA footprint than flight) includes enough testpoints to facilitate monitoring of the Z80-Core and an option for an external discrete Z80 processor. Logic analyzer and Debug-UART connectors included on the main board.

The ETU uses a dedicated "debug connector" that feeds the following signals to an auxiliary "debug board". The debug connector includes:

| Debug Connector Net Name | Function                              | Driven by                                     |

|--------------------------|---------------------------------------|-----------------------------------------------|

| MEMADDR(16:0)            | Memory Address Bus                    | DCB-FPGA                                      |

| MEMDATA(7:0)             | Memory Data Bus                       | Both (BiDIR I/O)                              |

| MBUSCYCTYPE(3:0)         | Debug decode (see below)              | DCB-FPGA                                      |

| MISCCNTL(11:0)           | Debug control/indicators (see below)  | Both (Split Inputs/Outputs)                   |

| LASTROBE(2:0)            | Logic Analyzer Clocks                 | DCB-FPGA                                      |

| DBG_NMI_PBSWITCH         | NMI Input to CPU (debounced in FPGA)  | Debug Board                                   |

| DBG_RESET_PBSWITCH       | RESET Input (debounced by RC circuit) | Debug Board                                   |

| RxD                      | Debug UART Receive Port               | Debug Board                                   |

| TxD                      | Debug UART Transmit Port              | DCB-FPGA                                      |

| Vcc_3.3                  | 3.3 V. Supply                         | connects to DCB supply<br>via series resistor |

| GND                      | Ground                                | to DCB ground                                 |

The ETU Debug configuration allows the z80 CPU to boot from either the on-board ROM or an external debug board based ROM. Four of the MISCCNTL signals are allocated for this purpose. The remaining eight MISCNTL signals are used for LEDs.

| Bus Assignment | Signal Name/Function | Comments                                                                               |

|----------------|----------------------|----------------------------------------------------------------------------------------|

| MISCCNTL(0)    | ALTBOOTREAD          |                                                                                        |

| MISCCNTL(1)    | ALTBOOTWRITE         |                                                                                        |

| MISCCNTL(2)    | ALTBOOTCS            |                                                                                        |

| MISCCNTL(3)    | ALTBOOTSEL           | Pulled up on DCB, Ground on Debug board via<br>jumper for debug board PROM boot select |

| MISCCNTL(7:4)  | DBG_LED(7:4)         | Debug board based LED indicators - upper nibble                                        |

| MISCCNTL(11:8) | DBG_LED(3:0)         | Debug board based LED indicators - lower nibble                                        |

The MBUSCYCTYPE, used to facilitate Logic Analyzer tracing is defined as follows:

| Bus Assignment   | Signal Name/Function | Comments                                    |

|------------------|----------------------|---------------------------------------------|

| MBUSCYCTYPE(3)   | MBUS RD/WR           | $1 \Rightarrow$ READ; $0 \Rightarrow$ WRITE |

| MBUSCYCTYPE(2)   | MBUS DMA/CPU Cycle   | 1=> CPU; 0 => DMA                           |

| MBUSCYCTYPE(1:0) | MBUS CYCLE DEF       | During DMA access:                          |

|                  |                      | 00 => DFB                                   |

|                  |                      | 01 => TLM                                   |

|                  |                      | 10 => FSH                                   |

|                  |                      | 11 => CMD                                   |

|                  |                      | During CPU access:                          |

|                  |                      | 00 => SRAM                                  |

|                  |                      | 01 => PROM                                  |

|                  |                      | 10 => EEPROM                                |

|                  |                      | 11 => OTHER (CPU-FLASH or ADC)              |

LASTROBE(1:0) are driven by MBUS Read and Write Strobes. LASTROBE(2) is a spare.

L

#### 2.3.2 Interrupts

Unlike the 8085, the Z80 has a general interrupt signal designed for connection to one of the Z80 Peripheral Interrupt controllers. The "Mode 1" configuration provides one interrupt that vectors to 038H. Hardware subsystems that can interrupt the CPU are:

| Interrupt Source | Description                                       |

|------------------|---------------------------------------------------|

| TimerTick        | Latched version of the timing interrupt (256 Hz). |

| Telemetry DMA    | Latched version of TLM UART DMA done interrupt    |

| FLASH Memory DMA | FLASH Memory DMA                                  |

The various interrupt sources are ORed together; the CPU can determine which interrupt(s) are active by reading the Status flags. Any of the three interrupts can be enabled/disabled by software, allowing the CPU to run in polled or interrupt driven mode on a per subsystem basis.

The proto and debug boards include an NMI Interrupt pushbutton switch, debounced by the FPGA.

### 2.4 CPU Memory

The CPU bus is directed by the FPGA to a memory bus containing a boot ROM (32Kx8 CMOS device), an external SRAM (128Kx8), and a EEPROM (128Kx8). (The EEPROM also contains internal protection mechanisms as well as an FPGA administered "write-protect".) At reset, the processor fetches from address 0, where boot ROM is mapped. When the ROMON bit is cleared, SRAM is mapped into the lower section of CPU memory, but ROM is still accessible at an upper location in the linear memory map (so it can be used to store canned parameters, tables, etc.).

ROM and EEPROM accesses incur three wait states; SRAM accesses are zero wait states.

The Z80, with its 16-bit address bus, provides for a 64Kbyte memory space. In order to access the larger memory devices, the FPGA includes a memory paging mechanism, as described in the following section.

#### 2.4.1 CPU Memory Map

The FPGA decodes Z80 addresses as follows:

For memory accesses (when the Z80 signal IORQ=0), the mapping is:

\* Inst Space Decode: Lower 32K selects ROM only when ROMON = 1

Selects SRAM only when ROMON = 0

Following a reset, the ROMON bit (read-writable via the Control Register) is asserted. When ROMON = 1, memory accesses to the lower 32K result in a fetch from ROM. When ROMON = 0, the entire non-paged memory area maps to the lower 56K of SRAM.

The upper 8Kbytes of memory addresses the full linear memory map via two FPGA based Page Registers, writable via the register interface. The Page Registers, address pointers spanning MemAdr[28:12], default to zero at reset. With this configuration a data access to upper CPU addresses such as 0xE000 actually result in an access to SRAM address 0. This may be useful for copying from ROM to lower SRAM at startup.

A "Low-Half Write Protect" control prohibits CPU writes to the lower 32Kbytes of CPU memory. Upon reset, writes are enabled; in order to disable, the CPU sets a Write Disable Control Register bit. The Low-Half Write Protect applies to both paged and non-paged addressing modes. DMA writes are always prohibited from the lower half of SRAM. Both CPU and DMA SRAM write violations are flagged and available to the CPU as status.

#### 2.4.1.1 Full Linear Memory Map

Lower memory address are directly driven by the processor; upper memory address and chip selects are determined by the Page Registers.

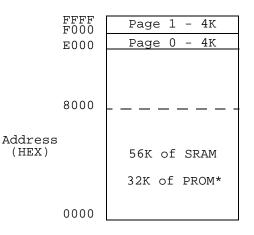

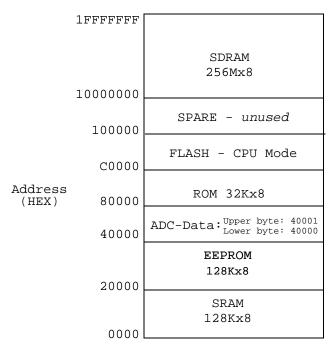

The full linear map of external memory is shown below:

#### FIGURE 2. DCB Full Linear Memory Map

The Page Registers, along with the CPU address, are used to select a region in the linear memory map. The 17-bit Page Registers define pointers for MemAdr[28:12] of the Linear Memory Array. Note: bit 28 selects SDRAM.

Smaller devices (such as ADC-Data and FLASH CPU Mode) alias within their regions.

Accesses to unused areas result in a no-op bus cycle (normal bus cycle termination, but no chip selects are generated). Similarly, if SDRAM is accessed when powered off, a no-op cycle occurs.

Note: the upper quadrant SDRAM is reserved for ECC check-bits when Error Correction is enabled.

#### Null Accesses

If the CPU performs an access to an undefined area of the memory map, the bus control subsystem performs a 0 wait state cycle, but treats the access as a "No-op". No chip selects are generated and reads will return indeterminate data. Accesses to SDRAM when the SDRAM has not been activated are treated as null accesses and flagged as such.

#### 2.4.2 CPU I/O Space

Z80 I/O space, selected with IORQ=0, is consists of DCB FPGA based registers devoted to the various DCB & IDPU subsystems (i.e. DCB Control, CDI Interface, Analog Housekeeping). Register definitions appear below:

#### **DCB-FPGA Register Definitions.**

I/O Addresses allocated to the DCB based registers, are defined below:

NOTE: Unless otherwise noted, DCB-FPGA Register based counters start counting at zero.

| Addr<br>(hex) | Read Register                                                         | Write Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10            | Control (dcbCtl) - same as write value                                | Control (dcbCtl) -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|               |                                                                       | Bit 7 - Spare<br>Bit[6:4]: Interrupt Enables (all<br>default to 0, disabled, at reset)<br>Bit 6 - Enable FLASH DMA int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               |                                                                       | Bit 5 - Enable Tlm Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               |                                                                       | Bit 4 - Enable Timer Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|               |                                                                       | <ul> <li>Bit 3 - Memory Low Half Write disable <ul> <li>prohibits CPU writes to the</li> <li>lower half of Z80 memory space</li> <li>(DMA writes are always blocked</li> <li>from this region). Defaults to 0,</li> <li>writes enabled.</li> </ul> </li> <li>Bit 2 - EEPROM write enable - defaults <ul> <li>to 0, writes disabled</li> </ul> </li> <li>Bit 1 - SDRAM Power: Controls 3.3V <ul> <li>Power to SDRAM array and associated</li> <li>buffers. Default is 0 at</li> <li>power on reset SDRAM off. (NOT</li> <li>cleared by watchdog reset.)</li> </ul> </li> <li>Bit 0 - ROMON - Boot ROM Disable: Controls mapping of the Boot ROM; <ul> <li>reset (power on or watchdog)</li> <li>default is 1, ROM enabled</li> </ul> </li> </ul> |

| 11            | Page Register 0 $(PgReg0Lo)$ - Lower Bits - same as write value       | Page Register 0 (PgRegOLo) - Lower Bits<br>Bit[7:0] - CPU MemPage Addr[19:12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12            | Page Register 0 $(PgReg0Hi)$ - Upper Bits - same as write value       | Page Register 0 (PgReg0Hi) - Upper Bits<br>Bit[7:0] - CPU MemPage Addr[27:20]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13            | Page Register 0 $(PgReg0SD)$ - SDSel - same as write value            | Page Register 0 (PgReg0SD) - SDSel<br>Bit[0] - CPU MemPage Addr[28]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14            | Page Register 1 (PgReg1Lo) - Lower Bits<br>- same as write value      | Page Register 1 (PgReg1Lo) - Lower Bits<br>Bit[7:0] - CPU MemPage Addr[19:12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15            | Page Register 1 $(PgReg1Hi)$ - Upper Bits - same as write value       | Page Register 1 (PgReg1Hi) - Upper Bits<br>Bit[7:0] - CPU MemPage Addr[27:20]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16            | Page Register 1 $(PgReg1SD)$ - SDSel - same as write value            | Page Register 1 (PgReg1SD) - SDSel<br>Bit[0] - CPU MemPage Addr[28]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 18            | DIAG Port - (LEDReg/SwitchStat) -                                     | DIAG Port - (LEDReg) -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               | Bits[7:0] - SWITCH(7:0) (proto)<br>Bits[7:0] - LEDS[7:0] (ETU/Flight) | Bits[7:0] - LED(7:0) (ETU/Flight & proto)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Addr       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (hex)      | Read Register                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Write Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1A         | <pre>Auxiliary Status (aux_Stat) -<br/>Bit[7] - Spare<br/>Bits[6:4] - Board ID (set via<br/>external jumpers)<br/>Bit[3] - SDRAM_Active - Indicates<br/>SDRAM is ready (power on and initial-<br/>ization complete)<br/>Bit[2] - SDRAM Null Cycle - Indicates<br/>that a subsystem attempted and SDRAM<br/>access prior to SDRAM activation<br/>Bit[1] - CDI (DFB Cmd) Busy - CMDBUSY<br/>Bit[0] - CDI(DFB Cmd) CMDAVERRDET -<br/>Interface Error Detect Flag</pre> | spare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18         | <pre>Status Register (statReg)<br/>Bit[7] - Watchdog Reset Detect<br/>Bit[6] - DMA LH Mem Write Err Detect<br/>Bit[5] - CPU LH Mem Write Err Detect<br/>Bit[4] - CPU Bus Null Cycle Detect<br/>Bit[3] - Latched CLK1HZ (Sample Time)<br/>Bit[2] - Latched S/C PulErrDet<br/>Bit[1] - Latched SpinPulDet (from S/C)<br/>Bit[0] - Latched 1PPS Det (from S/C)</pre>                                                                                                   | <pre>Pulse Register (pulReg) - Writing to<br/>this register with the appropriate<br/>bit(s) set causes the following<br/>actions:<br/>Bit[7] - Clear Latched Watchdog Reset<br/>Detect<br/>Bit[6] - spare<br/>Bit[5] - Clear Latched DFB Interface<br/>Error Detect Flag (CMDAVERRDET)<br/>Bit[4] - Clear Memory Error Detect<br/>(clears CPU Bus Null Cycle, CPU LH<br/>Mem Write Err, DMA LH Mem Write Err<br/>and SDRAM Null Cycle detects)<br/>Bit[3] - Clear Latched CLK1HZ<br/>Bit[2] - Clear Latched S/C PulErrDet<br/>Bit[1] - Clear Latched SpinPulDet<br/>Bit[0] - Clear Latched 1PPS Det</pre> |

| 1C         | Interrupt Status Register (intStatReg)<br>Bit[2] - Latched TIMInt<br>Bit[1] - Latched TLMDMAInt<br>Bit[0] - Latched FLASHDMAInt                                                                                                                                                                                                                                                                                                                                     | Interrupt Clear Register (intClrReg)-<br>Bit[2] - Clear Latched TIMInt<br>Bit[1] - Clear Latched TLMDMAInt<br>Bit[0] - Clear Latched FLASHDMAInt                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1D -<br>1E | spare                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| lF         | FPGA Version Number (fpgaVers) -<br>Bits[7:0]<br>The protoboard FPGA Versions start at<br>0x80 (i.e. Rev. 0x84), the ETU-FLASH<br>Revs start at 0xC0                                                                                                                                                                                                                                                                                                                | Watchdog Reset Clear (WATCHDOG) - a<br>write of X5 (lower nibble = 5; upper<br>nibble is a don't cares) to this<br>address "stomps" on the watchdog<br>timer. This should be done at least<br>every 2 seconds in order to prevent a<br>watchdog reset.                                                                                                                                                                                                                                                                                                                                                    |

| 20         | Delta MET Latch Lo ( <b>dMETLo)</b> - (MET to<br>Sample Counter - low byte)<br>Bit[7:0] - Internal Counter[16:9]<br>(latched at the S/C 1PPS)                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21         | Delta MET Latch Hi ( <b>dMETHi</b> ) - (MET to<br>Sample Counter - high byte)<br>Bit[7] - Seconds (rollover)<br>Bit[6:0] - Internal Counter[23:17]<br>(latched at the S/C 1PPS)                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Addr<br>(hex) | Read Register                                                                                                                                                                                                             | Write Register                                                                                                                                                                                                                                                |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22            | <pre>Internal Counter Lo (ctrLo) - (Timebase<br/>Counter - low byte)<br/>Write (any data) to this address<br/>before reading the count<br/>Bit[7:0] - Internal Counter[16:9]<br/>(latched at write to this address)</pre> | (ctrLo) - Write of any data to this<br>address latches the Timebase counter                                                                                                                                                                                   |

| 23            | Internal Counter Hi (ctrHi) - (Timebase<br>Counter - high byte)<br>Bit[7] - Seconds (rollover)<br>Bit[6:0] - Internal Counter[23:17]<br>(latched at write to ctrLo address)                                               |                                                                                                                                                                                                                                                               |

| 24            | SpinPulse Time Lo (spTmLo)-<br>Bit[7:0] - Internal Counter[16:9]<br>latched at SpinPulse Detect                                                                                                                           |                                                                                                                                                                                                                                                               |

| 25            | SpinPulse Time Hi ( <b>spTmHi)</b> -<br>Bit[7] - Seconds (rollover)<br>Bit[6:0] - Internal Counter[23:17]<br>latched at SpinPulse Detect                                                                                  |                                                                                                                                                                                                                                                               |

| 26            | ADC Control (ADCCtl)<br>Bit[7] - ADC Shutdown - defaults to<br>zero (ADC in "nap mode") at reset<br>Bits[2:0] - AMUX address                                                                                              | ADC Control (ADCCtl) -<br>Bit[7] - ADC Shutdown - defaults to<br>zero (ADC in "nap mode") at reset<br>Bits[2:0] - AMXCH[2:0] - AMUX address                                                                                                                   |

| 27            |                                                                                                                                                                                                                           | ADC Conversion Start (ADC_CONV) -<br>Any write to this address pulses the<br>SOC line of the ADC, causing a conver-<br>sion. Data can subsequently be read<br>back via Memory Mapped Registers<br>(see Figure 2, "DCB Full Linear Memory<br>Map," on page 11) |

| 28            | <pre>Inst Cmd - DatLo - (CDIDatLo)- Bits[7:0] - CommandData (bits 7:0 of the 24 bit command word)</pre>                                                                                                                   | <pre>Inst Cmd - DatLo - (CDIDatLo)- Bits[7:0] - CommandData (bits 7:0 of the 24 bit command word)</pre>                                                                                                                                                       |

| 29            | Inst Cmd - DatHi - (CDIDatHi)-<br>Bits[7:0] - CommandData (bits 15:8<br>of the 24 bit command word)                                                                                                                       | Inst Cmd - DatHi - (CDIDatHi)-<br>Bits[7:0] - CommandData (bits 15:8<br>of the 24 bit command word)                                                                                                                                                           |

| 2A            | <pre>Inst Cmd - Command ID (CDIID)- Bits[7:0] - CommandData (bits 7:0 of the 24 bit command word).</pre>                                                                                                                  | <pre>Inst Cmd - Command ID (CDIID) - Bits[7:0] - CommandID (bits 23:16 of the 24 bit command word)</pre>                                                                                                                                                      |

| 2B            |                                                                                                                                                                                                                           | Command Start (CDIStart) -<br>Writing any value to this register<br>starts the shift of the previously<br>loaded command.<br>(NOTE: The DFB CDI Registers (ID,<br>Command Data and CDIStart) should not<br>be written to when CMDBUSY bit is                  |

|               |                                                                                                                                                                                                                           | asserted. If this occurs, the writes<br>are ignored and the and error flag,<br>CMDAVERRDET, is set)                                                                                                                                                           |

|               |                                                                                                                                                                                                                           | (Command I/F Status is available at the AuxStat Register)                                                                                                                                                                                                     |

| 2C            | <pre>PCBCmdData (PCBCmdDat) Bits[7:0] - CmdDat to be shifted to the PCB</pre>                                                                                                                                             | PCBCmdData (PCBCmdDat)<br>Bits[7:0] - CmdDat to be shifted to<br>the PCB                                                                                                                                                                                      |

| Addr<br>(hex) | Read Register                                                                                                                                                                                           | Write Register                                                                                                                  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 2D            | PCB Command (PCBCmdStat)                                                                                                                                                                                | PCB Command (PCBCmd) -                                                                                                          |

| 20            | Bit[1] - PCB Command Error (set if<br>PCBCmdStart is issued illegally, in<br>which case the command is ignored)                                                                                         | <pre>Bit[1] - ClrPCBCmdErr - Writing a one<br/>clears the PCB Command Error Flag<br/>Bit[0] - PCBCmdStart - Writing a one</pre> |

|               | Bit[0] - PCB Command Interface Busy                                                                                                                                                                     | starts the shift of the data previ-<br>ously loaded into the PCBCmdDat<br>Register if the interface is not<br>busy.             |

| 2E –<br>2F    | spare                                                                                                                                                                                                   |                                                                                                                                 |

| 30            | ECC Control (eccCtl)                                                                                                                                                                                    | ECC Control (eccCtl) -                                                                                                          |

|               | Bit 7 - ECCSTATE -status (0-> scrubber<br>has not yet completed initialization)                                                                                                                         | Bits[7:4] - not used<br>Bits[3:2]: ECC Subsystem Scrub Period                                                                   |

|               | Bit 6 - ScrubCSErrDet - Scrubber Chip<br>Select Error detect - status feedback<br>indicating that an SDRAM client has<br>attempted to use the scrubber segment<br>(upper quadrant) when ECC is enabled. | as follows:<br>0 -> 7.68µs<br>1 -> 250µs<br>2 -> 2ms<br>3 -> "ON-DEMAND"                                                        |

|               | Cleared by ECCErrClr<br>Bits[5:4] - ECC Scrubber Upper Address<br>- ScrubAddr[27:26] (also see Regs<br>ECCAdrn)                                                                                         | Default is 0 at Reset.<br>Bit 1 - Scrub Test Mode - Defaults to<br>zero at reset - 0-> Normal Mode,<br>1 -> Test Mode           |

|               | Bits[3:0] same as write values                                                                                                                                                                          | Bit 0 - Scrub Enable - Defaults to zero at reset, scrubbing disabled.                                                           |

| 31            | ECC SingleBit ErrCnt (SBErr)-<br>Bits[7:0] - SBErrCnt[7:0]                                                                                                                                              | ClearECCErrs (ECCErrClr) -<br>Writing any data to this address the<br>ScrubCSErrDet (read back at address<br>30)                |

|               |                                                                                                                                                                                                         | NOTE: ECCErrClr is asserted during SDRAM power-off periods.                                                                     |

| 32            | ECC MultBit ErrCnt (MBErr) -                                                                                                                                                                            | ECCScrub Pulse (ECCScrPul) -                                                                                                    |

|               | Bits[7:0] - MBErrCnt[7:0]                                                                                                                                                                               | Writing any data to this addresses<br>causes a scrub cycle to occur when<br>scrub period is set to "ON DEMAND"                  |

| 33            | ECC CheckBit Register (ECCCkBitsJam)                                                                                                                                                                    | ECC CheckBit Register (ECCCkBitsJam) (used in testmode)                                                                         |

|               |                                                                                                                                                                                                         | Bits[7:0] - ECCCkBitsJam[7:0]<br>Bit 7: Tag Bits[6:0]: Checkbits                                                                |

| 34            | ECC Scrubber Address (ECCAdr0)-<br>Bits[7:0] - ScrubAddr[9:2] - Scrubber<br>Status feedback - running address<br>pointer (longwords)                                                                    |                                                                                                                                 |

| 35            | ECC Scrubber Address (ECCAdr1)-<br>Bits[7:0] - ScrubAddr[17:10] -<br>Scrubber Status feedback                                                                                                           |                                                                                                                                 |

| 36            | ECC Scrubber Address (ECCAdr2)-<br>Bits[7:0] - ScrubAddr[25:18] -<br>Scrubber Status feedback                                                                                                           |                                                                                                                                 |

| 37            | ECC Last Checkbits Read (ECCCkBitsRd)-<br>Bits[7:0] - ECCCkBitsRd[7:0] -<br>Scrubber Status feedback                                                                                                    |                                                                                                                                 |

| Addr<br>(hex) | Read Register                                  | Write Register                                                                                                                                     |

|---------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 40            | TLM Control Register (TLMStat) -               | TLM Control Register (TLMCtl)-                                                                                                                     |

|               | Bit[6] - PageAddr[28]                          | Bit[6] - PageAddr[28]                                                                                                                              |

|               | Bit[5] - Aliveness Status Flag                 | - MSBit of Next PageAddress                                                                                                                        |

|               | Bit[4] - Power Down Request Flag               | Bit[5] - Aliveness Status Flag to be<br>inserted into next packet                                                                                  |

|               | Bit[3] - Spare<br>Bit[2] - TLMBCErrDet         | Bit[4] - Power Down Request Flag to be<br>inserted into next packet                                                                                |

|               | Bit[1] - TLMBQErrDet                           | Bit[3] - Spare                                                                                                                                     |

|               | Bit[0] - Enable TLM - reads back as<br>written | Bit[2] - Clear Error Detects<br>(TLMBCErrDet & TLMBQErrDet) - pulse                                                                                |

|               |                                                | Bit[1] - Start Transmission of next<br>queued TLM-Buffer - pulse                                                                                   |

|               |                                                | Bit[0] - Enable TLM - defaults to 0,<br>disabled (which holds the TLM sub-<br>system in a reset state)                                             |

| 41            | TLM Page Lo (TLMPAdrLo) - same as              | TLM Page Lo (TLMPAdrLo) -                                                                                                                          |

|               | write value                                    | PageAddress of Next TLM Tlm Buffer                                                                                                                 |

|               |                                                | Bits[7:0] - TLM Page[19:12]                                                                                                                        |

| 42            | TLM Page Hi (TLMPAdrHi) - same as              | TLM Page Hi (TLMPAdrHi)-                                                                                                                           |

|               | write value                                    | PageAddress of Next TLM Tlm Buffer                                                                                                                 |

|               |                                                | Bits[7:0] - TLM Page[27:20]                                                                                                                        |

| 43            | TLM Length Lo (TLMLenLo) - same as write value | TLM Length Lo (TLMLenLo) - Length (in<br>Longwords) of Next TLM Tlm Buffer<br>(Reminder: Program to #Longwords - 1)<br>Bits[7:0] - TLM Length[7:0] |

| 44            | TLM Length Hi (TLMLenHi) & State               | TLM Length Hi (TLMLenHi)-                                                                                                                          |

|               | Bits[6:4] - TLM State                          | Length of next TLM Tlm Buffer                                                                                                                      |

|               | 000 -> IDLE; nonzero -> Active                 | Bits[1:0] - TLM Length[9:8]                                                                                                                        |

|               | Bits[1:0] - TLM Page[9:8]                      |                                                                                                                                                    |

| 45-<br>47     | spare                                          | spare                                                                                                                                              |

| 48            | TLM Tlm - CurAdr- B0 (TLM0CAdr)                |                                                                                                                                                    |

| -             | (Current Address Pointer)                      | NOTE: TLM Current address is a                                                                                                                     |

|               | Bits[7:2] - TLMCurAddr[7:2]                    | dynamic value and may change during                                                                                                                |

| 49            | TLM Tlm - CurAdr - B1 (TLM1CAdr)               | <ul> <li>the period required to read all four<br/>bytes. The FSW should make allow-</li> </ul>                                                     |

|               | Bits[7:0] - TLMCurAddr[15:8]                   | ances for this possibility; when the                                                                                                               |

| 4A            | TLM Tlm - CurAdr - B2 (TLM2CAdr)               | buffer is actively being read out,                                                                                                                 |

|               | Bits[7:0] - TLMCurAddr[23:16]                  | the lower byte will increment                                                                                                                      |

| 4 <b>B</b>    | TLM Tlm - CurAdr - B3 (TLM3CAdr)               | approximately every 350µs at<br>115KBaud                                                                                                           |

| Δr            | Bits[4:0] - TLMCurAdr[28:24]                   |                                                                                                                                                    |